Inconvenientes de la división entre niveles

El establecimiento de niveles de abstracción en el estudio de un computador hace posible acotar su complejidad al utilizar metodologías de análisis y síntesis propias en cada nivel, permitiendo que dentro de un nivel el usuario pueda abstraerse de lo que ocurre en los demás niveles. Este planteamiento que facilita sin duda el estudio del computador presenta sin embargo algunas dificultades cuando se contempla el problema de la optimización.

En efecto, a la hora de implementar una especificación no sólo deben cumplirse todos los requerimientos funcionales de la misma, además se deben optimizar ciertas funciones de calidad que generalmente tienen que ver con la velocidad (maximización) y el costo (minimización). En efecto, existen ocasiones en las que contemplar tan solo los niveles frontera de un nivel en el que se plantea un problema de diseño puede dar lugar a la imposibilidad de optimizar la implementación.

A título de ejemplo citaremos dos casos en los que se presenta esta situación. El primero entre los niveles eléctrico y lógico, y el segundo entre los niveles lenguajes de alto nivel y arquitectura (repertorio de instrucciones).

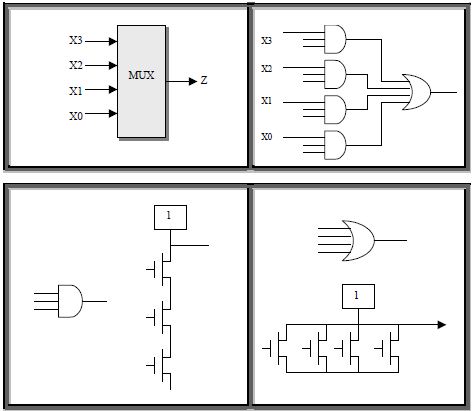

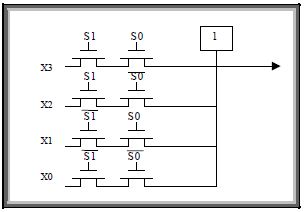

1) Niveles eléctrico <--> lógico Si nos planteamos el diseño de un multiplexor con conmutadores bidireccionales (tecnología NMOS estática) respetando los niveles de diseño, obtendríamos en primer lugar el esquema lógico (con puertas) del multiplexor, y después expresaríamos cada puerta lógica en términos de los conmutadores bidireccionales.

El diseño resultante es más costoso (mayor número de conmutadores) que el que podemos obtener si planteamos el diseño directamente con conmutadores:

2) Niveles lenguaje de alto nivel <--> arquitectura

En este caso un compilador, para optimizar el código máquina que genera (mayor velocidad), tiene en cuenta no sólo la arquitectura (repertorio de instrucciones) sino la forma en que se ejecutan estas instrucciones (estructura) en la ruta de datos de la máquina. Este hecho puede dar lugar a que el orden de las instrucciones máquina generadas no sea el orden lógico que utilizaría un programador de lenguaje máquina que ignorase los detalles estructurales de la arquitectura. Esta situación viene producida fundamentalmente por la segmentación y paralelización de las instrucciones dentro de la máquina y se estudiará con detalle en las asignaturas de Ampliación de Estructura de Computadores y Arquitectura e Ingeniería de Computadores.

Fuente: Estructura de Computadores, Facultad de Informática, UCM