Memoria virtual paginada

El mecanismo de traducción de DV a DF que acabamos de describir corresponde a un sistema de memoria virtual paginada. En él el espacio virtual (y físico) se divide en páginas de igual tamaño.

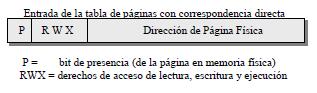

Veremos en el apartado siguiente otra alternativa en la que la MV se divide en segmentos de longitud variable, dando lugar a la memoria virtual segmentada. Las entradas de la TP de una MV paginada, además del NPF contiene unos bits de control, de los que hemos mencionado el bit de presencia P.

Como se muestra en la siguiente figura, existen otros bits que controlan los derechos de acceso a la página: lectura (R), escritura (W) y ejecución (X), este último sólo para páginas de código. También suele existir un bit que indica si la página ha sido modificada (datos) y necesita escribirse en disco cuando sea sustituida. En general, los demás bits de control dependen de cada procesador.

Cada programa (proceso) puede ocupar una gran cantidad de memoria virtual. Por ejemplo, en la arquitectura VAX, cada proceso puede tener hasta 231 = 2 GBytes de memoria virtual. Utilizando páginas de 2 9 = 512 bytes, eso significa que se necesitan tablas de páginas de 222 entradas por proceso. La cantidad de memoria dedicada sólo a tablas de páginas podría ser inaceptablemente alta.

Para solucionar este problema, la mayoría de los esquemas de memoria virtual almacenan las tablas de páginas en la propia memoria virtual, en lugar de utilizar la memoria física. Esto significa que la tabla de páginas también está sujeta a paginación, igual que el resto de los programas. Cuando un programa se está ejecutando, al menos una parte de su tabla de páginas, incluyendo el elemento correspondiente a la página actualmente en ejecución, debe estar en la memoria principal.

Fuente: Estructura de Computadores, Facultad de Informática, UCM