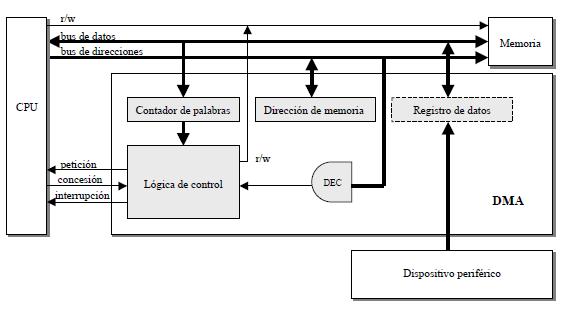

Para gestionar las transferencias de información, un controlador de DMA dispone de 3 registros: datos, dirección y contador de palabras.

El registro de dirección almacena la dirección de la siguiente palabra a transmitir, incrementándose de forma automática después de cada transferencia.

El contador de palabras almacena el número de palabras que quedan por transmitir y también se decrementa automáticamente después de cada transferencia.

La lógica de control comprueba el contenido del contador de palabras y finaliza la operación cuando alcanza el valor 0. Un decodificador se encargará de identificar la dirección de memoria asignada al DMA . La CPU debe enviar, pues, la siguiente información al DMA cuando quiera realizar una operación de E/S:

• El sentido de la operación de E/S: lectura o escritura

• La dirección del periférico

• La posición de memoria donde comienza el bloque a leer o escribir

• El número de palabras que componen el bloque

Transmitida esta información, la CPU pasa a realizar otra tarea, delegando totalmente la operación de E/S al DMA. El DMA transfiere directamente, palabra a palabra, el bloque de datos entre el periférico y la memoria, sin pasar por la CPU. Cuando la transferencia finaliza el DMA envía una señal de interrupción a la CPU.

Para poder transferir a/desde la memoria, el DMA necesita controlar el bus durante un tiempo suficiente para completar la transferencia. Sin embargo, este tiempo no tiene que ser continuo, puede fraccionarse en pequeños intervalos que se alternan con la CPU.

Existen diferentes alternativas en la forma de controlar el bus.

Cada alternativa supone un compromiso diferente entre velocidad de transferencia y actividad de la CPU. El empleo de una alternativa en concreto dependerá de las prestaciones que se deseen y de las características del procesador que se utilice.

Fuente: Estructura de Computadores, Facultad de Informática, UCM