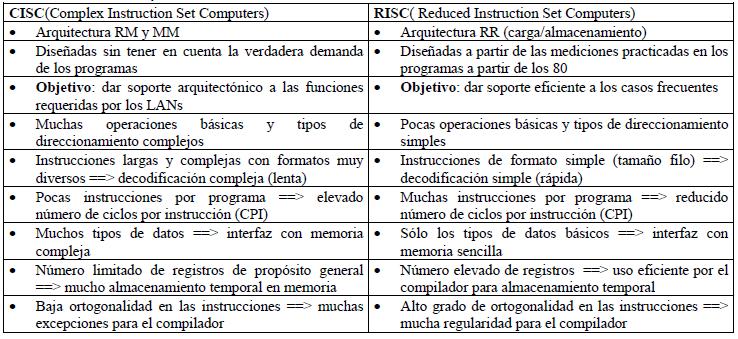

Características comparativas

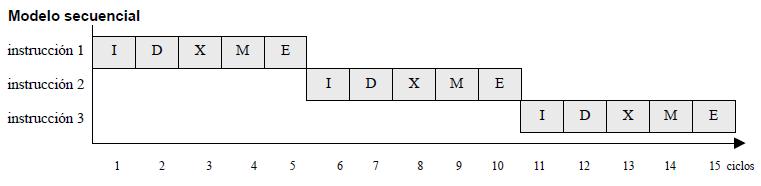

Segmentación

Una de la ventajas de los procesadores RISC es la facilidad que presentan sus instrucciones para ser ejecutadas de forma segmentada, es decir, solapando dos o más fases de ejecución.

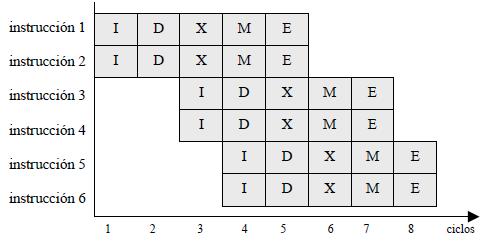

La tarea de cada instrucción se divide en etapas, de tal forma que en cada ciclo se ejecuta una etapa de una instrucción, simultaneándose la ejecución de etapas de diferentes instrucciones.

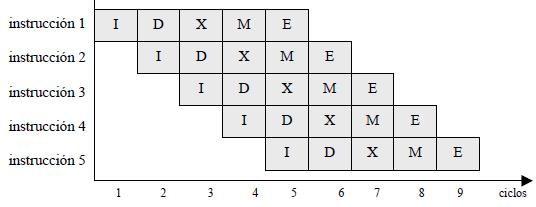

Modelo segmentado lineal

Los primeros RISC tenían un modelo de ejecución segmentado lineal en el que todas las instrucciones pasan por las mismas etapas y en cada ciclo entra una nueva instrucción a ejecutar.

Modelo infrasegmentado

En cada n ciclos se lanza una nueva instrucción (Stanford MIPS). Esto está motivado fundamentalmente porque el tiempo de ciclo no permite acceder a algunos recursos hardware como la memoria, por lo que se necesitan dos (o más) ciclos para acceder a la misma.

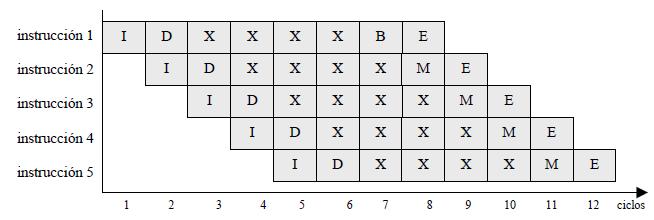

Modelo supersegmentado

Aumentan el rendimiento disminuyendo el tiempo de ciclo. Esto lo consiguen aumentando considerablemente el número de etapas del procesador (o dividiendo la etapa en subciclos).

Con ello se consigue que el rendimiento máximo del procesador aumente; pero tiene un inconveniente que va a afectar considerablemente al rendimiento real: el aumento de las latencias de las instrucciones inducido por el aumento del número de conflictos entre las instrucciones que tengan algún tipo de dependencia a la hora de la ejecución (dependencias de datos, estructurales o de control), con la consiguiente pérdida de rendimiento.

Modelo superescalar

Para aumentar el rendimiento el modelo superescalar lanza a ejecutar en cada ciclo n instrucciones a la vez, siendo n el orden o grado del superescalar.

Sin embargo, para que se puedan lanzar a ejecutar a la vez n instrucciones no debe haber conflictos entre ellas. Éste es un factor que va a limitar, de forma significativa, el rendimiento, y es una medida del paralelismo implícito que presentan las aplicaciones y que pueden extraer los compiladores.

Fuente: Estructura de Computadores, Facultad de Informática, UCM