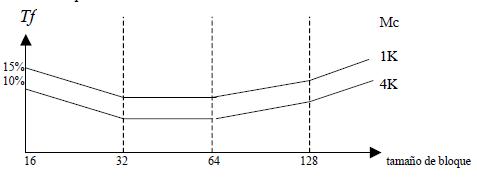

La tasa de fallos podemos reducirla con las siguientes alternativas:

a) Aumento del tamaño del bloque

• Al aumentar el tamaño de bloque disminuye la tasa de fallos iniciales (forzosos) porque mejora la localidad espacial.

• Sin embargo con el aumento del tamaño de bloque aumenta la penalización de fallos, ya que el tiempo de lectura y transmisión serán mayores si los bloques son mayores.

b) Aumento de la asociatividad

• Experimentalmente se comprueba que una caché asociativa por conjuntos de 8 vías es tan eficiente (tasa de fallos) como una caché completamente asociativa.

• Una caché de correspondencia directa de tamaño N tiene aproximadamente la misma tasa de fallos que una asociativa por conjuntos de 2 vías de tamaño N/2

• Al aumentar la asociatividad se incrementa el ciclo de reloj y por tanto Tacierto

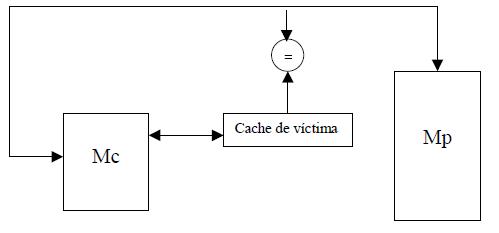

c) Utilización de una caché de víctimas

• Se añade una pequeña caché completamente asociativa entre Mc y su camino hacia Mp para contener sólo los bloques descartados (sustituidos) por un fallo (víctimas)

• Ante un fallo se comprueba si el bloque está en la caché de víctima antes de acudir a Mp

• Reducen los fallos de conflicto fundamentalmente en cachés pequeñas con correspondencia directa.

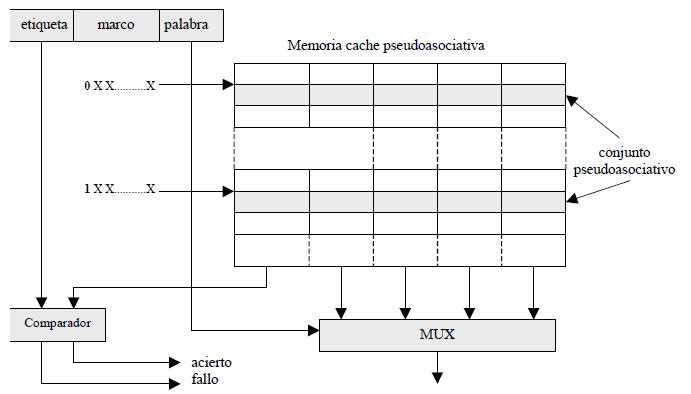

d) Cachés pseudoasociativas

Se trata de cachés de correspondencia directa que con una ligera modificación se pueden comportar como asociativas. Para ello se permite que un bloque de Mp se pueda ubicar en dos (pseudoasociativa de 2 vías) marcos de bloque de Mc, el que le corresponde (por la correspondencia directa) y el que resulta de conmutar el bit más significativo de la dirección del bloque, tal como se indica en el siguiente esquema:

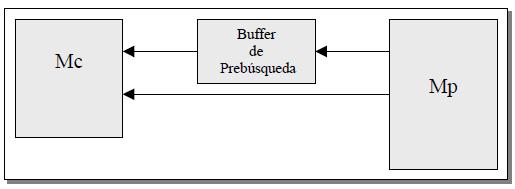

e) Prebúsqueda de instrucciones y datos

• La prebúsqueda de instrucciones y/o datos antes de ser demandados por la caché disminuye la tasa de fallos.

• Las instrucciones o datos prebuscados son llevados directamente a la caché o a un buffer externo que es accedido a mayor velocidad que Mp

• El Alpha AXP 21064 pre-busca dos bloques cuando ocurre un fallo, el que contiene la palabra causante del fallo y el siguiente. El primero lo coloca en MC y el segundo en el buffer de prebúsqueda

• Experimentalmente se ha comprobado que un buffer de prebúsqueda simple elimina el 25 % de los fallos de una caché de datos con correspondencia directa de 4 KB

f) Prebúsqueda controlada por el compilador

• Utiliza instrucciones explícitas de prebúsqueda del tipo prefetch(dato) que el compilador utiliza para optimizar los programas después de realizar un análisis de sus sentencias.

• La prebúsqueda se realiza al tiempo que el procesador continúa la ejecución del programa, es decir, la prebúsqueda se hace en paralelo con la ejecución de las instrucciones.

• Los bucles son las construcciones más apropiadas para que el compilador genere prebúsqueda

g) Optimizaciones del compilador

Las optimizaciones consisten en transformaciones del código fuente del programa realizadas en tiempo de compilación con el objetivo de aumentar la localidad espacial y/o temporal del programa, y consiguientemente reducir la tasa de fallos. Entre las transformaciones más importantes estudiaremos las siguientes:

• Fusión de arrays

Se sustituyen varios arrays de igual tamaño por un único array de elementos estructurados. La transformación aumenta la localidad espacial si el programa referencia localmente las componentes de igual índice de los arrays originales.

Fuente: Estructura de Computadores, Facultad de Informática, UCM