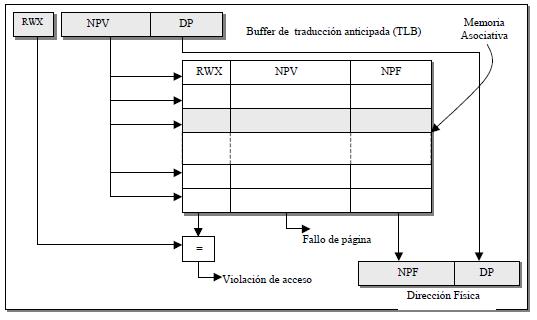

En principio toda referencia a memoria virtual requiere dos accesos a la memoria física: uno para acceder al elemento de la TP, y otro para acceder a la memoria física. Por tanto, un esquema de memoria virtual como el que acabamos de estudiar duplicaría el tiempo de acceso a memoria.

Para evitar este inconveniente los esquemas de memoria virtual utilizan una cache especial para los elementos de la TP, llamada usualmente buffer de traducción anticipada (TLB, Translation Lookaside Buffer).

El TLB funciona lo mismo que una memoria cache, y contiene aquellas entradas de la TP a las que se han accedido recientemente. Por el principio de localidad temporal, la mayoría de las referencias a memoria corresponderán a posiciones incluidas en páginas recientemente utilizadas.

Por ese motivo, la mayoría de las referencias involucran a entradas de la TP presentes en el TLB. Normalmente el TLB utiliza una correspondencia totalmente asociativa, por lo que una entrada de la TP puede ubicarse en cualquier posición del TLB.

Fuente: Estructura de Computadores, Facultad de Informática, UCM