En la E/S programada el procesador tiene que esperar un tiempo considerable a que el módulo de E/S esté preparado para realizar la operación. El procesador espera comprobando repetidamente el estado del módulo de E/S, degradándose significativamente el rendimiento de la CPU. Para evitar este inconveniente se introdujo el sistema de interrupciones en los procesadores.

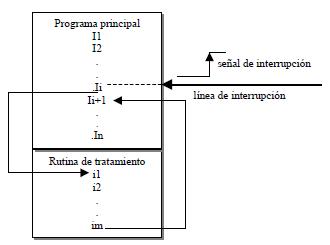

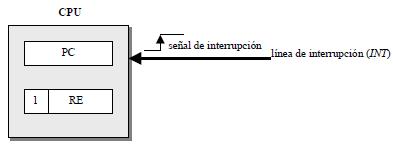

Básicamente una interrupción viene determinada por la ocurrencia de una señal externa que provoca la bifurcación a una dirección especifica de memoria, interrumpiendo momentáneamente la ejecución del programa. A partir de esa dirección se encuentra la rutina de tratamiento que se encarga de realizar la operación de E/S propiamente dicha, devolviendo después el control al punto interrumpido del programa.

Podemos, pues, ver una interrupción como un salto a subrutina (rutina de tratamiento) ocasionado por una señal externa, y no por una instrucción del programa. De esta forma se pueden eliminar los tiempos muertos de consulta de la E/S programada

La implementación de un sistema de interrupciones implica introducir una fase de consulta de las líneas de interrupción al final de la ejecución de cada instrucción. En un procesador sin sistema de interrupciones, se podría conseguir un efecto similar introduciendo una instrucción de consulta y la correspondiente de salto sobre el valor de la consulta, detrás de cada instrucción natural del programa.

De esta forma se garantizaría la respuesta al dispositivo de E/S en el momento que pasa a estado disponible, al tiempo que la CPU ejecuta instrucciones útiles del programa. El precio a pagar sería el recargo introducido por la ejecución de las parejas de instrucciones de consulta y salto introducidas detrás de cada instrucción útil del programa. Sería algo así como una E/S programada en la que en lugar de preguntar en el mismo punto del programa por el estado del periférico, se replica la consulta por todo el programa, intercalándose con la ejecución de las instrucciones útiles.

Pues bien, un sistema de interrupciones podemos verlo como la integración en hardware del supuesto software anterior, es decir, la integración de la consulta y posible salto dentro de la ejecución de cada instrucción del repertorio.

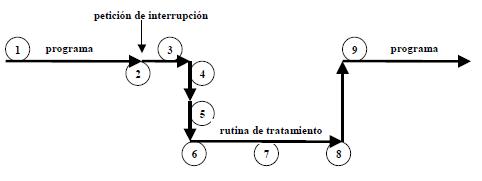

El mecanismo de interrupción de un procesador tiene que implementar todas las medidas que hagan que se pueda bifurcar a la rutina de tratamiento y recuperar el estado del programa interrumpido cuando la rutina finaliza su ejecución. En el siguiente esquema se detallan las fases que tienen lugar en la atención a una interrupción producida por algún dispositivo periférico:

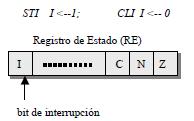

(1) El programa en ejecución (CPU) activa el sistema de interrupciones utilizando instrucciones que operan (ponen a 1 y a 0) sobre el bit de capacitación de las interrupciones I del registro de estado (RE):

(2) Se produce la petición de interrupción por parte de algún dispositivo periférico en un instante de tiempo impredecible para la CPU

(3) La CPU finaliza la ejecución de la instrucción en curso.

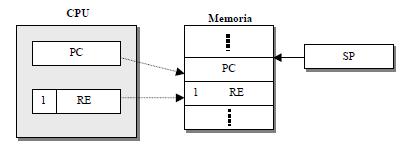

(4) La CPU salva automáticamente el estado en la pila, es decir, el contador de programa (PC) y el registro de estado (RE):

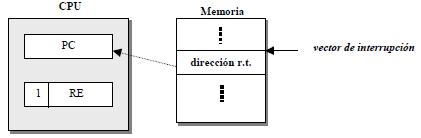

(5) La CPU obtiene la dirección de la rutina de tratamiento a partir del vector de interrupción (VI), que usualmente se ubica en memoria.

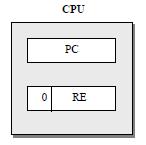

(6) La CPU descapacita las interrupciones (I = 0) para que durante la ejecución de la primera instrucción de la rutina de tratamiento no se vuelva a detectar la misma interrupción y provoque un bucle infinito.

(6) La CPU ejecuta la rutina de tratamiento de la interrupción que realiza lo siguiente:

- Salva en la pila los registros a utilizar

- Realiza la operación de Entrada/Salida

- Restaura desde la pila los registros utilizados

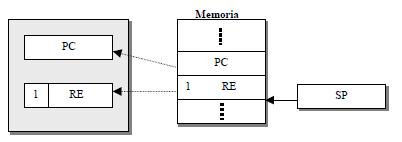

(8) Finaliza la rutina de tratamiento con la ejecución de la instrucción de retorno de interrupción (RTI), que restaura automáticamente el estado de la CPU desde la pila y vuelve al programa interrumpido:

(9) La CPU continúa la ejecución del programa interrumpido, quedando las interrupciones capacitadas automáticamente al recuperarse el valor I = 1 del RE.

Fuente: Estructura de Computadores, Facultad de Informática, UCM