En este tipo de E/S no existe un reloj común entre el emisor (módulo de E/S) y el receptor (dispositivo), aunque ambos utilizan señales locales de reloj para generar (emisor) y muestrear (receptor) la información, señales con valores de frecuencia nominalmente iguales.

El estado de reposo de la línea de tranmisión serie es en alta. El emisor comienza la transmisión con un bit de start de valor 0 cuyo flanco negativo detecta el receptor como inicio de una transmisión.

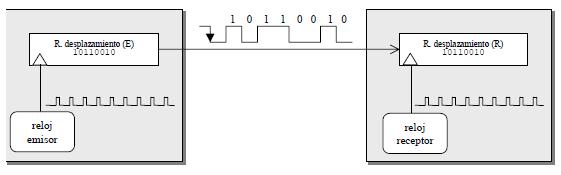

A partir de ese momento el emisor transmite en forma serie los bits de datos de su registro de salida (que es un registro de desplazamiento) a una frecuencia marcada por su reloj local (reloj emisor). El receptor muestrea la línea con una frecuencia nominalmente igual a la del emisor sobre su registro de entrada (que es otro registro de desplazamiento).

Como ambos relojes son físicamente diferente, no se evita que con el tiempo se vaya desplazando uno respecto al otro, con el riesgo que si los bits transmitidos son muchos el receptor los muestree incorrectamente.

Sin embargo, como emisor y receptor se resincronizan con el bit de start del siguiente caracter transmitido, y sólo se tranmite un caracter cada vez, estos deslizamientos no producen error.

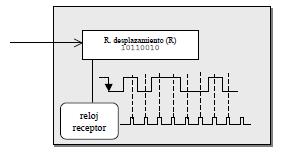

En la siguiente figura se muestra que el reloj local del receptor muestrea la línea de transmisión en instantes de tiempo correctos, es decir, dentro del intervalo de tiempo correspondiente a un bit (intervalo bit)

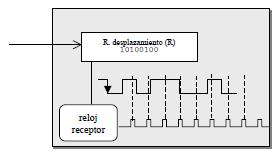

En cambio, si el reloj local del receptor tiene una frecuencia ligeramente inferior (mayor período), como se muestra en la siguiente figura, a partir del cuarto intervalo bit la señal será muestreada incorrectamente en el receptor.

Fuente: Estructura de Computadores, Facultad de Informática, UCM