La memoria virtual debe interactuar con la memoria cache (no con la cache que implementa el TLB, sino con la cache de la memoria principal).

Para traducir una DV el sistema de memoria consulta el TLB para comprobar si la entrada de la TP se encuentra en él. Si es así, se genera la dirección real (física), combinando el NPF con el DP. Si no, se accede a la TP en busca del elemento correspondiente. Una vez que se ha generado la dirección física, compuesta por una etiqueta y un número de conjunto, se consulta la cache para ver si el bloque que contiene la palabra referenciada se encuentra en dicho conjunto. Si es así, se envía al procesador. Si no, se produce un fallo de cache y se busca la palabra en memoria principal.

Por tanto, la dirección virtual debe pasar primero por el TLB antes de que la dirección física pueda acceder a la cache, lo que alarga el tiempo de acierto. Este mecanismo se puede acelerar utilizando dos alternativas:

1. Acceder en paralelo (simultáneamente) al TLB para buscar el NPF y al directorio de la cache para buscar el bloque.

2. Utilizar caches con direcciones virtuales

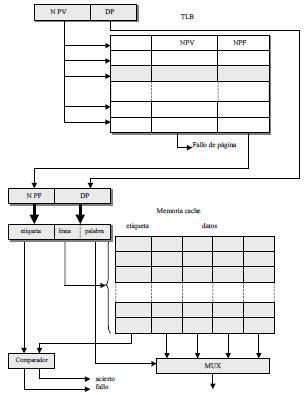

La primera alternativa requiere que la longitud del campo de desplazamiento DP de la DV (igual al DP de la DF) sea mayor o igual que los campos de conjunto y palabra del formato de la DF para la cache, tal como se muestra en la siguiente figura.

De esta forma será posible realizar en paralelo la búsqueda en el TLB del NPF que se corresponde con la etiqueta, y en el directorio de la cache el nº de bloque (línea), que junto a la palabra dentro del bloque, se corresponde con el DP, del que se dispone desde el instante que se genera la DV, pues no requiere traducción.

Esto significa que el tamaño de la cache viene impuesto por el tamaño de la página y el grado de asociatividad. Por ejemplo, si tenemos un tamaño de página de 1K, el DP tendrá 10 bits. Si el número de palabras por bloque es 8 (3 bits de palabra) quedarán 7 bits para el campo de conjunto de la dirección física de la cache. Si la asociatividad fuese 1 (correspondencia directa) con esos 7 bits podríamos distinguir tan sólo entre 128 marcos de bloque o líneas de la cache, lo que impondría un tamaño de cache de 128 x 8 = 1024 = 1K.

Para aumentar este tamaño tendríamos que aumentar la asociatividad. Por ejemplo, si el grado de asociatividad es 2, el tamaño de la cache sería de 2K. Cuando aumenta el grado de asociatividad, también aumentan las comparaciones que debemos realizar con la etiqueta obtenida del TLB, ya que se deben comparar con ella todas las etiquetas del conjunto de la cache (tantas como vías)

La segunda alternativa de utilizar caches direccionadas virtualmente tiene la ventaja de que en caso de acierto en la cache, no es necesario el proceso de traducción. Sin embargo, esta alternativa tiene dos problemas fundamentales.

El primero surge en las conmutaciones de procesos. Cuando se cambia de proceso, la misma dirección virtual de cada proceso referencia diferentes direcciones físicas, lo que exige que se limpie la cache y esto supone una gran fuente de fallos forzosos.

El segundo se origina porque es posible que distintos procesos con diferentes direcciones virtuales se correspondan con la misma dirección física (aliasing). Esto puede producir dos copias del mismo dato en una cache virtual, lo que ocasiona problemas de inconsistencia si hay escrituras.

Fuente: Estructura de Computadores, Facultad de Informática, UCM