La E/S de los computadores ha experimentado una continua evolución. Comenzó con la E/S controlada por programa. Le siguió la introducción de las interrupciones para evitar que la CPU malgastase su tiempo esperando la realización de las operaciones de E/S , aumentando el rendimiento global del sistema.

Posteriormente se introduce en el controlador de E/S la capacidad para acceder directamente a memoria a través del DMA. De esta forma se pueden transferir bloques de datos a/desde memoria sin intervención de la CPU, excepto al comienzo y al final de la transferencia.

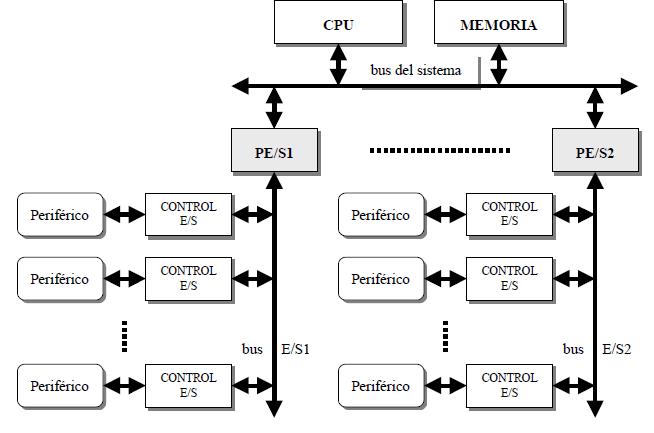

Pero este proceso de evolución de la E/S no termina en el DMA. En el paso siguiente se potencia la capacidad del controlador de E/S hasta convertirlo en un procesador con un conjunto de instrucciones especializadas en operaciones de E/S.

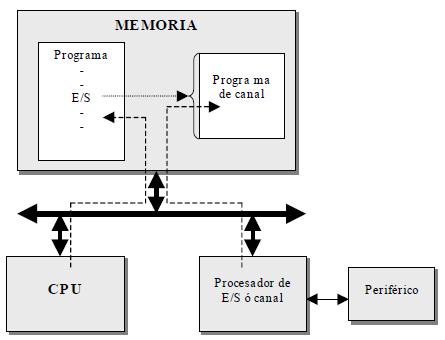

La CPU traduce las operaciones de E/S en órdenes dirigidas al procesador de E/S (PE/S) para que ejecute un programa de E/S residente en memoria. El PE/S ejecuta ese programa sin la intervención de la CPU y sólo se interrumpe cuando se ha ejecutado la secuencia completa. A los procesadores de E/S se les suele denominar también con el nombre de canales de E/S. No obstante los dos términos se emplean de forma indistinta.

Un PE/S representa, pues, una extensión del concepto DMA. Un PE/S tiene la capacidad de ejecutar instrucciones de E/S, lo que le da un control completo sobre dicha operación.

En los computadores que incluyen PE/S, la CPU no ejecuta las instrucciones de E/S, éstas se almacenan en memoria principal para ser ejecutadas por un PE/S. Así, la CPU inicia una transferencia de E/S al dar una orden al PE/S para que ejecute un programa en memoria. El programa especifica entre otras cosas las siguientes:

• El periférico (o periféricos) que interviene en la operación de E/S.

• Las zonas de memoria utilizadas en la transferencia

• Las acciones a realizar si se producen ciertas condiciones de error durante la transferencia.

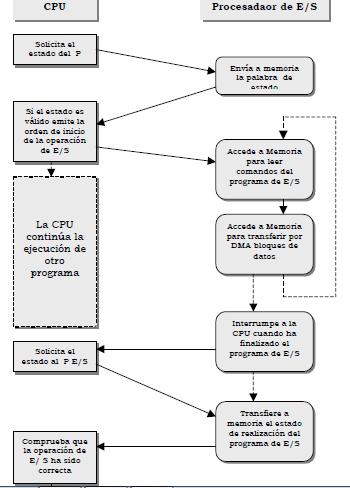

Las comunicaciones entre la CPU y el procesador de E/S a lo largo de la ejecución de una operación de E/S podemos resumirlas en el siguiente esquema:

Fuente: Estructura de Computadores, Facultad de Informática, UCM