En un DMA simple los parámetros relacionados con las transferencias de datos se cargan en los registros correspondientes utilizando instrucciones de E/S. En máquinas grandes que utilizan canales de E/S, esto se sustituye por el concepto de programa de canal.

El canal, como se ha dicho antes, es un pequeño procesador que tiene acceso a la memoria principal. Es capaz de ejecutar un conjunto limitado de instrucciones, conocidas como comandos de canal.

Estos comandos especifican aquellos parámetros que el canal necesita para controlar los dispositivos de E/S y realizar operaciones de transferencia de datos. Un programa de canal es una secuencia de estos comandos almacenada en la memoria principal.

La CPU inicia una operación de E/S con la emisión de una orden especial al canal que hace que el canal empiece a buscar en memoria y ejecutar los comandos que constituyen el programa de canal.

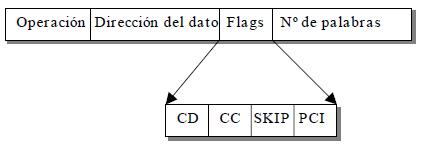

El programa de canal consta de una serie de palabras de comando de canal (CCW: channel command words) cuyo formato simplificado aparece en la siguiente figura:

Operación. Este campo corresponde al código de operación de las instrucciones máquina normales. Especifica la operación que debe realizar la CCW. La unidad de control decodifica este campo y envía las señales adecuadas de control al dispositivo. Existen varias operaciones, las más importantes son las siguientes:

Lectura: el canal transfiere a memoria principal un bloque de palabras de tamaño especificado en el campo nº de palabras, en orden ascendente de direcciones, empezando en la dirección especificada en el campo dirección del dato.

Escritura: el canal transfiere datos de memoria principal al dispositivo. Las palabras se transfieren en el mismo orden que en la operación de lectura.

Control: se utiliza esta orden para enviar instrucciones específicas al dispositivo de E/S, como rebobinar una cinta magnética, etc.

Bifurcación: cumple en el programa de canal la misma función que una instrucción de salto en un programa normal. El canal ejecuta las CCW en secuencia, salvo cuando aparece una CCW de este tipo, que utiliza el campo dirección del dato como la dirección de la siguiente CCW a ejecutar.

Flags Los bits de este campo indican lo siguiente:

1. CC (Encadenamiento de comando): cuando este bit está a 1, indica al canal que la siguiente CCW especifica una nueva operación de E/S que debe realizarse con el mismo dispositivo.

El canal ejecuta primero la operación de E/S especificada en la CCW que tiene a 1 el flag CC. Después ejecuta la siguiente sobre el mismo dispositivo. Desde el punto de vista del dispositivo, las dos operaciones resultantes de la primera y segunda CCW aparecen como dos comandos de E/S separados.

2. CD (Encadenamiento de datos): una CCW con el bit CD a 1, indica al canal que la siguiente CCW contiene una nueva dirección del dato y un nuevo nº de palabras. Éstos deben utilizarse para transferir un segundo bloque de datos hacia o desde el dispositivo de E/S, mediante la orden especificada por la CCW actual.

Cuando el canal termina la transferencia de datos especificada en la CCW con el bit CD a 1, no corta la conexión con el dispositivo de E/S, continúa la transferencia utilizando la dirección y el nº de palabras de la siguiente CCW. Con el encadenamiento de datos, los datos transferidos por la primera y segunda CCW aparecen como un bloque para el dispositivo de E/S. Esto facilita las transferencias entre un dispositivo y posiciones no contiguas de la memoria principal.

Para poner de manifiesto la diferencia entre encadenamiento de comandos y de datos veamos lo que ocurre con una transferencia de dos bloques de datos de la memoria principal a una cinta magnética. Si se utiliza encadenamiento de comandos, los dos bloques se escribirán en la cinta separados por un separador de registros que la unidad de cinta inserta de forma automática al final de una operación de E/S especificada por una CCW en donde CD = 0. En cambio, el encadenamiento de datos provoca que los dos bloques se unan en un solo registro en la cinta. Una CCW con los flags CD y CC a 0 significa el final del programa de canal.

3. SKIP (Salto): este bit, cuando está a 1, hace que el programa de canal salte un número de palabras igual al especificado en el campo nº de palabras. Cuando se utiliza con la orden de lectura, este flag hace que los datos se lean del dispositivo sin que se transfieran a la memoria principal.

4. PCI (Interrupción controlada por programa): el canal produce una interrupción cuando ejecuta una CCW con el flag PCI a 1. Si esta CCW va precedida por otra CCW con encadenamiento de comandos, la interrupción se genera después de que hayan concluido todas las transferencias de datos.

Fuente: Estructura de Computadores, Facultad de Informática, UCM