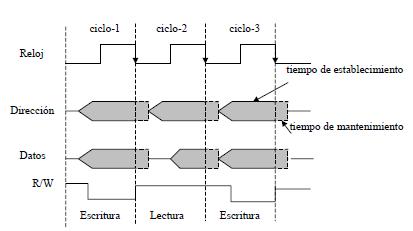

Síncronos

En los buses síncronos existe un reloj que gobierna todas las actividades del bus, las cuales tienen lugar en un número entero de ciclos de reloj. La transferencia propiamente dicha coincide con uno de los flancos del reloj (el de bajada en el ejemplo de la figura).

En este caso hemos supuesto que el tiempo de acceso al slave es menor de un ciclo, es decir, en cada ciclo tiene lugar una operación con memoria. Los buses síncronos son rápidos pero no tienen capacidad para conectar unidades con velocidad de transferencia baja. o no conocida a priori.

Asíncronos

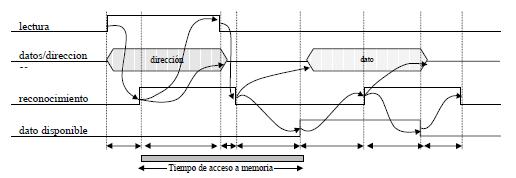

Los buses asíncronos utiliza un protocolo tipo handshaking para comunicarse el master con el slave.

En el siguiente diagrama se presenta el diálogo de señales que tiene lugar durante una transacción de lectura de memoria por parte de la CPU utilizando un protocolo asíncrono (handshaking) sobre un bus que multiplexa las direcciones y los datos sobre las mismas líneas (datos/dirección).

1) La CPU activa la señal de lectura al tiempo que coloca la dirección de la posición a leer en las líneas datos/dirección.

2) La Memoria detecta la activación de lectura, lee la dirección que hay en datos/dirección y activa la señal de reconocimiento para indicar que ha detectado la orden de lectura.

3) la CPU detecta la activación de reconocimiento y en respuesta desactiva la señal de lectura y libera las líneas de datos/dirección.

4) La memoria detecta que se ha desactivado la señal de lectura y desactiva la señal de reconocimiento para dar por terminado el reconocimiento de la orden de lectura.

5) Cuando la memoria ha accedido al dato y lo tiene preparado lo pone en datos/dirección y activa la señal de dato disponible.

6) La CPU detecta que dato disponible está activa y procede a leer los datos del bus y activar la línea de reconocimiento para indicar que ya dispone del dato.

7) La memoria detecta la señal de reconocimiento, desactiva dato disponible y libera las líneas de datos/dirección.

8) Finalmente, la CPU al detectar que se desactiva dato disponible, desactiva, a su vez, la señal de reconocimiento, indicando que la transmisión ha finalizado.

A partir de este momento se puede iniciar una nueva transacción.

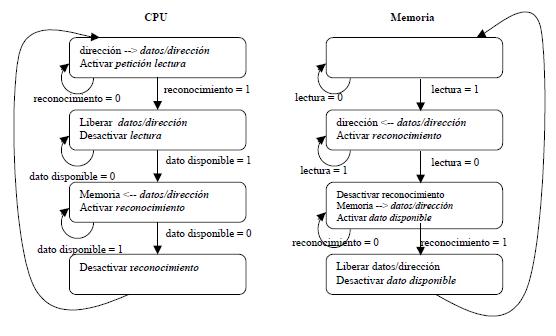

Un bus asíncrono trabaja igual que un par de máquinas de estados finitos que se comunican de tal forma que uno de los autómatas no avanza hasta que sabe que el otro autómata ha alcanzado un determinado estado, es decir, los dos autómatas están coordinados.

Los buses asíncronos se escalan mejor con los cambios de tecnología y pueden admitir una mayor variedad de velocidades de respuesta en los dispositivos.

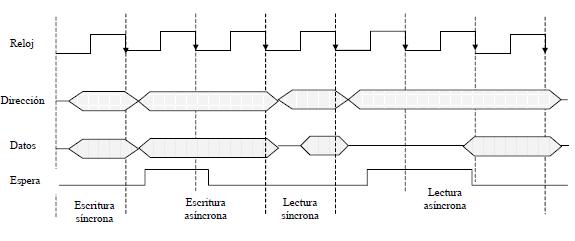

Semisíncronos

En los protocolos semisíncronos existe, como en los síncronos, un reloj que gobierna las transferencias en el bus. Sin embargo, en este caso existe, además, una señal de espera (wait) que es activada por el slave cuando la transferencia va a durar más de un ciclo de reloj. De esta forma, los dispositivos rápidos operarán como en bus síncrono, mientras que los lentos alargarán la operación el número de ciclos que les sea necesario.

Ciclo partido

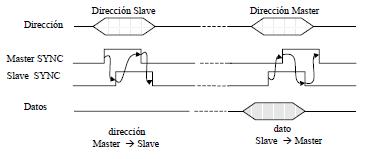

En los buses de ciclo partido la operación de lectura se divide en dos transacciones no continuas de acceso al bus. La primera transacción es la de petición de lectura que realiza el master sobre el slave. Una vez realizada la petición el master abandona el bus. Cuando el slave dispone del dato leído, inicia un ciclo de bus actuando como master para enviar el dato al antiguo master, que ahora actúa como slave.

Fuente: Estructura de Computadores, Facultad de Informática, UCM