En el MC 68000 las interrupciones se generalizan al concepto de excepción, que incluye las interrupciones hardware de E/S propiamente dichas, las producidas por eventos internos en la CPU, y las producidas por software.

Líneas de interrupción

Las excepciones de E/S llegan a la CPU en forma codificada a través de tres líneas externas: IPL2 , IPL1, IPL0, que codifican la ausencia de excepción (111), y 7 niveles con prioridad (000 el más prioritario y 110 el menos prioritario).

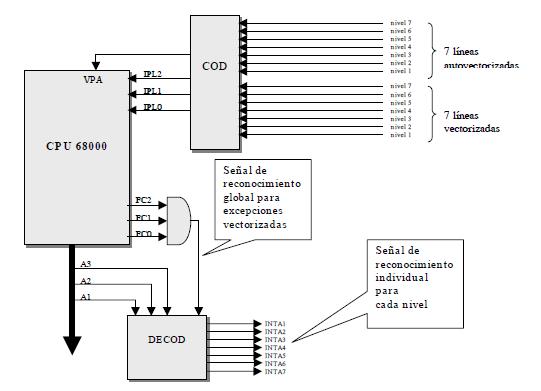

Una cuarta línea, VPA, determina si los siete niveles de las líneas IPLi codifican una excepción autovectorizada (VPA = 0) o vectorizada (VPA = 1). En el primer caso el vector de excepción es fijo para cada nivel, y en el segundo lo determina el periférico y lo transmite por las 8 líneas menos significativas del bus de datos cuando le llega la señal de reconocimiento procedente de la CPU, que corresponde al valor 111 de las señales de estado FC2, FC1, FC0. El número de la línea vectorizada reconocida lo genera la CPU a través de las líneas del bus de direcciones A3, A2, A1. Por ello, es necesario complementar con circuitería lógica externa el sistema, tal como aparece en el siguiente esquema:

Fuente: Estructura de Computadores, Facultad de Informática, UCM