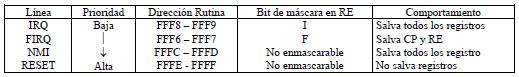

El MC 6809 dispone de las siguientes líneas de interrupción:

Veremos como se puede transformar la línea IRQ en 8 líneas de interrupción diferentes. Para ello se aprovecha el que cuando se produce una interrupción por esta línea y es atendida por la CPU, ésta accede a su vector de interrupción que se encuentra en las direcciones FFF8 y FFF9, lo que significa que en el bus de direcciones aparecerán estas direcciones.

Sólo en respuesta a una interrupción por IRQ se generan estas direcciones en el bus, por lo que podemos identificarla por hardware y descomponerla en 8 pares diferentes, una por cada línea nueva de interrupción.

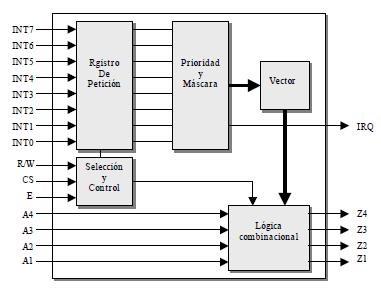

El esquema completo de un dispositivo que realiza esta conversión lo hemos representado en la siguiente figura. El dispositivo se selecciona cuando se activa la señal CS, por lo que esta señal deberá generarse cuando en el bus aparezcan las direcciones FFF8 y FFF9. Cuando eso ocurra, el dispositivo transformará las 4 líneas menos significativas del bus de direcciones (A4,A3,A2,A1) en otras 4 (Z4,Z3,Z2.Z1) de manera que en las Zi se genere uno de los 8 pares de las nuevas direcciones, el correspondiente a la línea INTi activada de mayor prioridad.

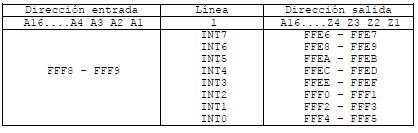

La tabla de transformación de direcciones sería, pues, la siguiente:

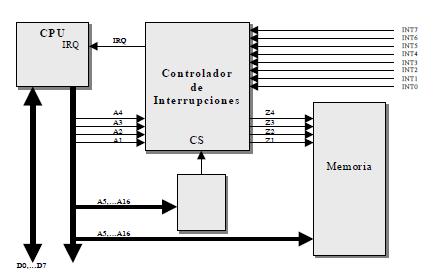

La disposición del controlador de interrupciones respecto a la CPU y la memoria se muestra en el siguiente esquema:

Fuente: Estructura de Computadores, Facultad de Informática, UCM