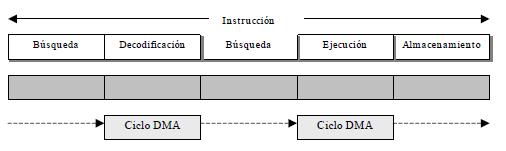

El DMA accede al bus sólo en los ciclos en los que la CPU no lo utiliza. Y esto ocurre en diferentes fases de ejecución de las instrucciones. De esta forma la ejecución del programa no se ve afectado en su velocidad de ejecución.

En los sistemas con memoria cache también se puede aprovechar el acceso de la CPU a la cache para que el DMA pueda acceder simultáneamente a la memoria principal. En resumen, los pasos que se siguen en la transferencia mediante DMA son:

1. La CPU ejecuta las instrucciones de E/S que cargan los registros de dirección y contador de palabras del controlador de DMA. El registro de dirección debe contener la dirección base de la zona de memoria principal que se va a utilizar en la transferencia de datos. El registro contador de palabra almacena el número de palabras que se transfieren desde/hacia la memoria.

2. Cuando el controlador de DMA está preparado para transmitir datos, activa la línea de petición. La CPU espera a un punto de concesión del DMA, renuncia al control de los buses de datos y direcciones y activa la línea de reconocimiento de DMA.

3. El DMA transfiere directamente los datos a/desde memoria principal por alguno de los métodos que se acaban de ver. Después de transferir una palabra, el registro de dirección y el registro contador de palabras del controlador se incrementa y decrementa respectivamente.

4. Si el contenido del registro contador de palabra no es 0, pero el periférico no está preparado para enviar o recibir los siguientes datos, el DMA devuelve el control a la CPU liberando el bus del sistema y desactivando la línea de petición. La CPU responde desactivando la línea de reconocimiento de DMA y continuando con su operación normal.

5. Si el contenido del contador de palabras es 0, el controlador de DMA renuncia al control del bus del sistema y envía una señal de interrupción a la CPU.

Fuente: Estructura de Computadores, Facultad de Informática, UCM