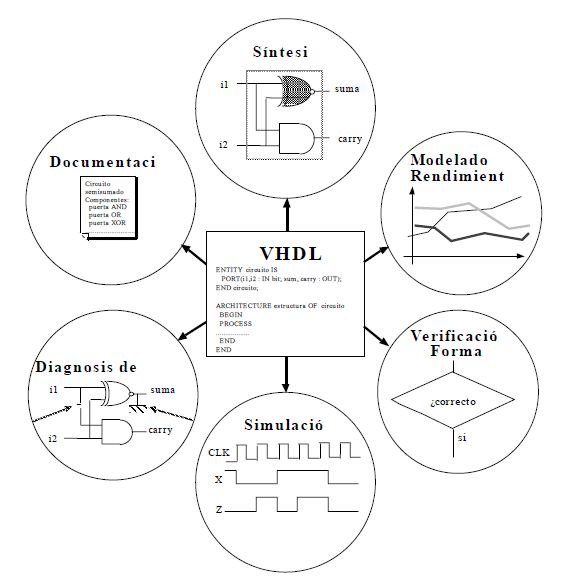

La síntesis automática tiene como objetivo la generación de dispositivos digitales a partir de una especificación inicial expresada en un lenguaje de descripción hardware. VHDL, al ser un lenguaje con una semántica poco formal, en el que se pueden mezclar diferentes estilos de descripción, no es el más apropiado para utilizar como entrada en las herramientas de síntesis. Sin embargo, dado su status de estándar IEEE y su amplia aceptación en la industria electrónica, resulta muy conveniente no romper el ciclo de diseño saliendo de VHDL en la fase de síntesis. Por ello, lo que se realiza habitualmente en este terreno es definir subconjuntos sintetizables de VHDL. En este sentido cabe distinguir dos grandes subconjuntos. Uno que engloba las construcciones secuenciales de VHDL, utilizado para la síntesis de alto nivel, y otro que parte de unas construcciones concurrentes de VHDL que permiten descripciones de dispositivos a nivel de transferencia de registros (RTL), utilizado para la síntesis de bajo nivel.

La diagnosis de fallos en circuitos digitales se puede plantear a partir de las descripciones VHDL de los mismos. En efecto, en lugar de identificar la parte de circuito que falla, podemos localizar la parte de descripción VHDL cuya implementación hardware tiene un fallo físico y está causando el fallo de comportamiento observado. En principio esta diagnosis es similar a la que se realiza a nivel de puertas, pero en este caso el nivel de descripción hardware puede ser más alto y consecuentemente el modelo de fallos será diferente.

La verificación formal de un diseño consiste en probar que para todos los estados iniciales aceptables y para todas las entradas posibles, la implementación del diseño cumple su especificación. Las otras dos alternativas para verificar un diseño, la síntesis automática y la simulación funcional, pueden resultar incompletas. En efecto, los diseños producidos por síntesis automática son correctos por construcción si los componentes primitivos están completamente verificados y si las transformaciones realizadas en el proceso de síntesis son así mismo correctas. Sin embargo, probar la corrección formal de un método de síntesis implica probar la corrección formal del método en sí y del software que lo implementa, tarea que puede resultar impracticable. Por otra parte, la verificación funcional por simulación exhaustiva también es impracticable a partir de una complejidad media en el diseño. La verificación formal requiere un modelo matemático para representar las propiedades bajo estudio y un cálculo para realizar computación simbólica sobre el modelo. La lógica es la rama de las matemáticas más ampliamente utilizada en la verificación formal, incluyendo la lógica de predicados de primer orden, la lógica de orden superior y la lógica temporal. Al no existir una semántica formal para VHDL los sistemas de verificación formal, al igual que los sistemas de síntesis, se limitan a subconjuntos del lenguaje.

Los modelos de rendimiento constituyen el nivel más alto de abstracción de los sistemas electrónicos. Estos modelos se utilizan principalmente para estudiar la capacidad global de procesamiento de información de un sistema en las primeras etapas del proceso de diseño. El objetivo es identificar las principales unidades funcionales y definir su forma de actuación en la transformación de los datos de entrada en datos de salida. A este nivel de conceptualización el diseñador ve una unidad funcional como algo que realiza una cierta tarea en un cierto tiempo, sin detalles específicos sobre la forma de realizar la tarea. En realidad, puede que estos detalles no se conozcan aún en esta fase del diseño. Debido a esta ocultación de detalles sobre los valores de los datos y sus transformaciones específicas se dice que los datos son no interpretados, y para resaltar este hecho a los modelos de rendimiento se les denomina a veces modelos no interpretados . VHDL, al disponer de recursos expresivos con alto nivel de abstracción, facilita la confección de modelos de rendimiento basados en redes de Petri extendidas y colas estocásticas.

Finalmente, la documentación es una de las tareas más importantes en todo proceso de diseño, y muy particularmente cuando el sistema tiene el grado de complejidad de los circuitos actuales. En estos casos se hace indispensable disponer de lenguajes con una elevada capacidad de abstracción y ampliamente aceptados por los diseñadores, como ocurre en la actualidad con VHDL.

Fuente: Estructura de Computadores, Facultad de Informática, UCM